应用材料公司公布的芯片布线创新将有助于解决节能计算方面的挑战。

芯片布线中使用新材料将使2nm节点制造成为可能,电路之间的宽度约为二十亿分之一米。这些创新将使布线电阻降低多达 25%,新材料将使芯片电容降低多达 3%。

值得一提的是,这是业界首次在量产中使用钌,使铜芯片布线能够扩展到 2nm 节点及以下。这个新型增强型低 k 介电材料也可降低芯片电容并增强逻辑和 DRAM 芯片的 3D 堆叠能力。

在机器规模上处理当今的威胁形势

芯片制造商目前正在利用逻辑芯片制造方面的进步,而内存芯片制造商(制造动态随机存取存储器或 DRAM)正在对其进行评估,以改进 3D 芯片堆叠。

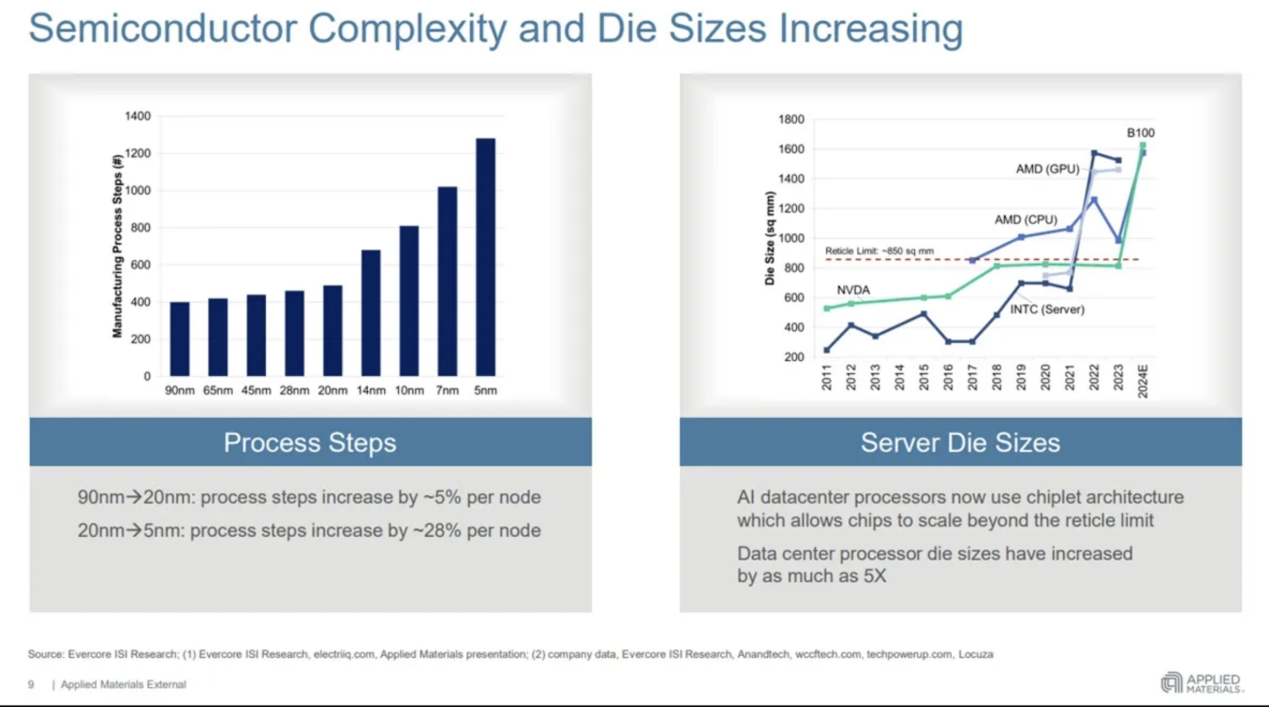

据IEEE Spectrum杂志报道,其最终目标是使设备能够构建万亿晶体管芯片,例如图形处理单元。很难跟上摩尔定律的步伐,这是英特尔前首席执行官戈登·摩尔在 1965 年预测的,该定律认为芯片上的元件数量每两年就会翻一番。芯片不但没有变小,反而越来越大,而且使用先进的封装技术,多个芯片被集成到一个解决方案中。

好消息是,过去 15 年来,芯片行业每两年就能实现三倍的进步。应用材料公司产品营销总监 Alex Jansen 在接受 VentureBeat 采访时表示,要做到这一点,就需要不断开发新材料。

“为了继续这一目标,我们需要新材料,”Jansen说。“有几种方法:图案化、晶体管、布线和先进封装。我们专注于布线。”

布线也很重要。他说,最近的芯片有超过 60 英里的铜互连、18 个金属层和四五个关键层。JanSEN说,每个芯片都是一个巨大的 3D 布线网络。

应用材料公司是最大的半导体制造设备制造商,该公司今天在旧金山举行的Semicon West活动上公布了这些进展。该公司表示,材料工程创新旨在通过使铜线扩展到 2nm 逻辑节点及以上来提高计算机系统的每瓦性能。

“AI时代需要更节能的计算,芯片的布线和堆叠对于性能和功耗至关重要。”应用材料半导体产品集团的Prabu Raja表示。他接着说:“应用材料公司最新的集成材料解决方案使业界能够将低电阻铜线扩展到新兴的埃节点,而我们最新的低 k 介电材料同时降低了电容并增强了芯片强度,将 3D 堆叠推向了新的高度。”

克服经典摩尔定律扩展的物理挑战

当今最先进的逻辑芯片可以容纳数百亿个晶体管,这些晶体管通过 60 多英里长的微型铜线连接起来。芯片的每一层布线都始于一层薄薄的介电材料薄膜,蚀刻后形成充满铜的通道。

几十年来,低 k 电介质和铜一直是业界最主要的布线组合,使芯片制造商能够在每一代产品中实现微缩、性能和功率效率的改进。

然而,随着行业规模缩小到 2nm 及以下,更薄的介电材料会导致芯片的机械性能下降,而铜线变窄会导致电阻急剧增加,从而降低芯片性能并增加功耗。

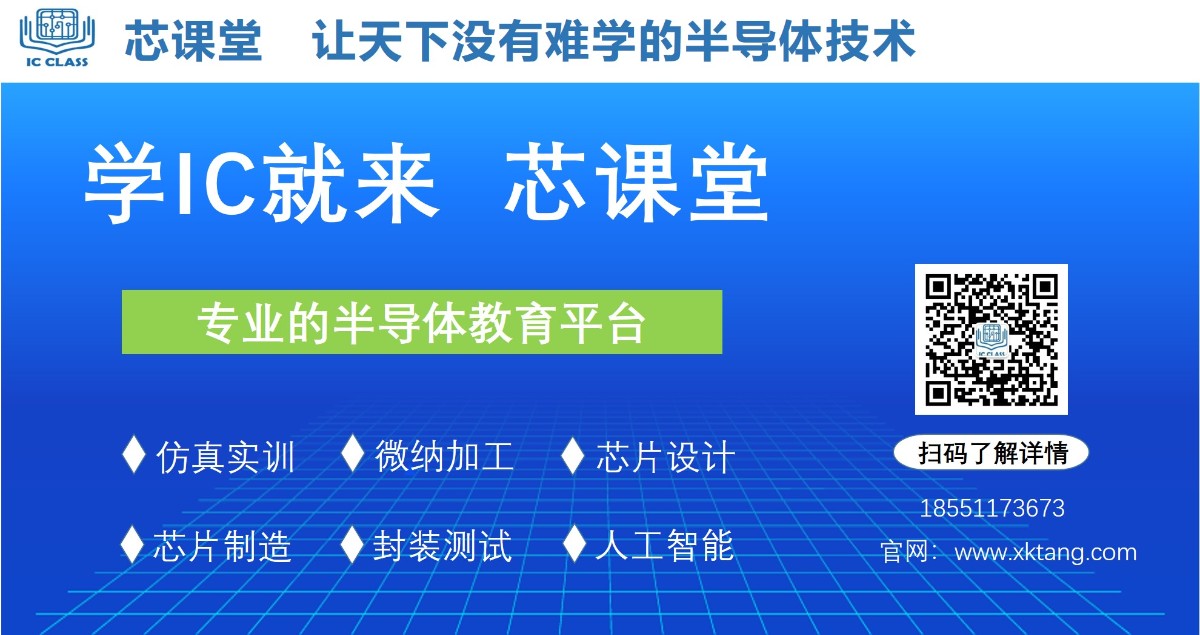

应用材料公司表示,其 Black Diamond 材料已引领行业数十年,该材料用低介电常数(或“k 值”)薄膜包裹铜线,旨在减少电荷的积累,从而减少功耗并导致电信号之间的干扰。

应用材料公司今天推出了增强版 Black Diamond,这是该公司 Producer Black Diamond PECVD(等离子增强化学气相沉积)系列的最新产品。这种新材料降低了最小 k 值,使其能够微缩至 2nm 及以下,同时提供更高的机械强度,这在芯片制造商和系统公司将 3D 逻辑和内存堆叠推向新高度时变得至关重要。

产品营销总经理 Ajay Bhatnagar 在接受 VentureBeat 采访时表示,电介质沉积小组一直在致力于解决电容方面的问题。

他说道:“我们非常高兴能够推出增强型Black Diamond的最新创新成果。”

它是一种新型化学气相沉积材料,用于支撑沟槽和将电线与二元材料隔离。

“你可以把它想象成一个矩阵,铜线网格嵌入其中,”Bhatnagar 说道。“我们用非常低 k 介电常数的薄膜包裹电线。这种薄膜的设计目的是为了减少电荷的积累,避免增加功耗并导致电信号相互干扰。”

“今天,我们推出了一种我们称之为增强型的新型Black Diamond。这种新材料的主要优点是降低了介电常数的关键值,使客户能够将其缩小到 2 纳米及以下,”Bhatnagar 说道。“但与此同时,它提高了机械强度,这现在变得非常非常关键。随着芯片制造商和系统公司将 3D 逻辑和内存堆叠推向新的高度,机械强度和价值变得非常关键。”

他说,增强型 Black Diamond 技术目前已被所有领先的逻辑和内存芯片制造商采用。

Bhatnagar 表示:“对于这种矩阵,我们在低 k 材料方面面临的最大挑战之一就是打破介电常数和机械强度之间的平衡。客户希望介电常数越来越低,因为这有助于降低电容和线路之间的信号噪声。”

“降低介电常数和提高电介质的机械强度之间存在着一种权衡。我们在分子水平上设计的这种新材料打破了这种既有的权衡。我们利用分子工程技术在这个基质上创造了一种新的低 k 材料,它打破了这种权衡。”

“我们正试图降低电容,而降低介电常数是降低电容的方法之一。电容与介电常数成正比。我们在降低介电常数的同时,也在提高机械强度,”Bhatnagar 说道。“通常,这需要权衡。因此,我们在增强型 Black Diamond 中添加了这种新分子,从而打破了这种权衡,并改变了曲线。”

新型二元金属衬里可实现超细铜线

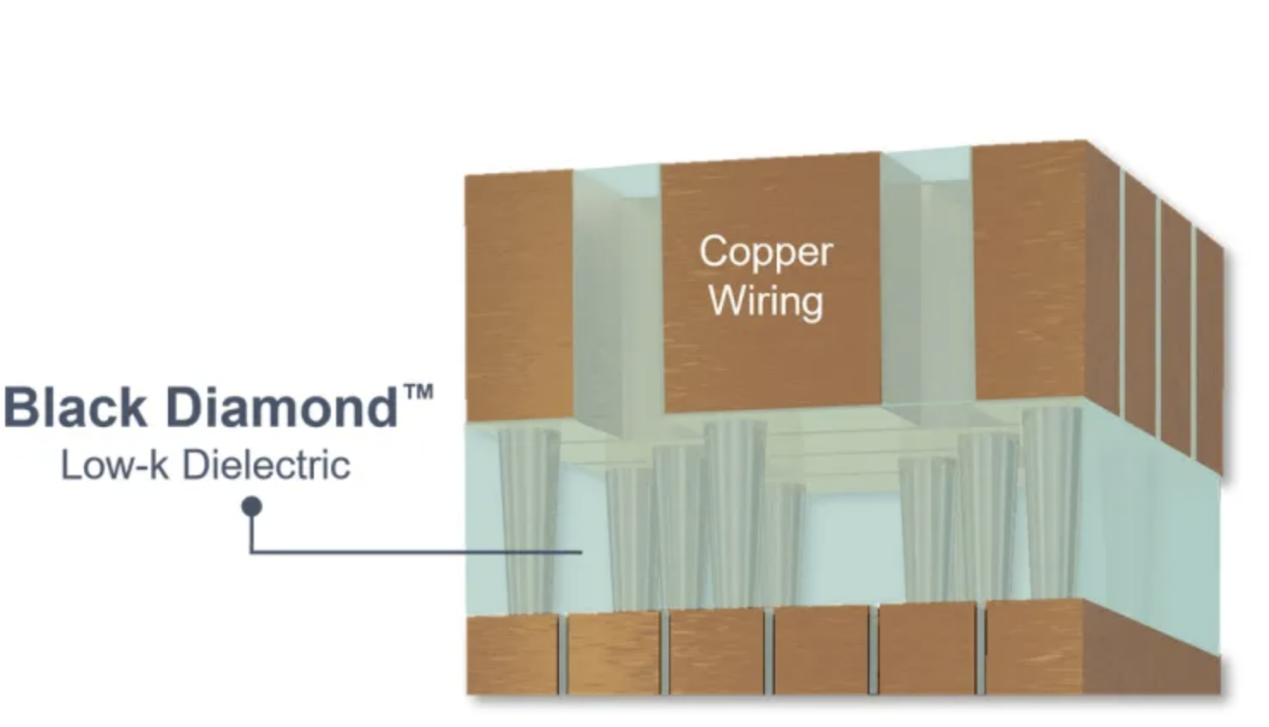

为了缩小芯片布线,芯片制造商蚀刻每一层低 k 薄膜以创建沟槽,然后沉积一层阻挡层,防止铜迁移到芯片中并造成产量问题。然后在阻挡层上涂上一层衬垫,以确保在最后的铜回流沉积序列中粘附,该序列会慢慢用铜填充剩余体积。

随着芯片制造商进一步缩小布线尺寸,阻挡层和衬里占据了布线空间的更大比例,在剩余空间中创建低电阻、无空隙的铜线在物理上变得不可能。

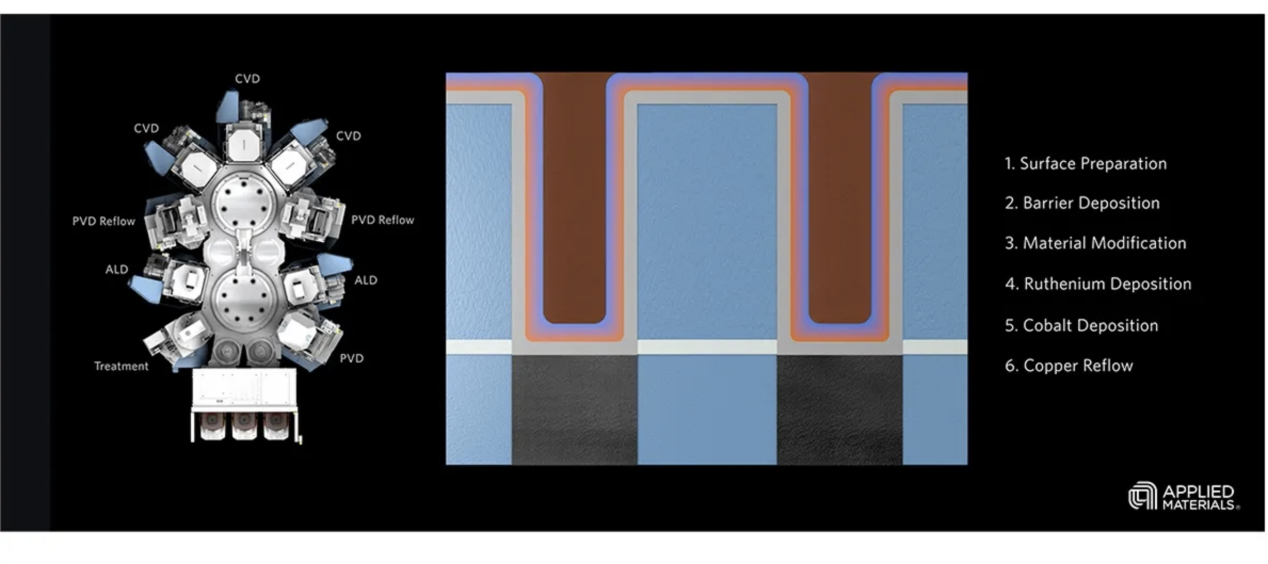

今天,应用材料公司推出了最新的 IMSTM(Integrated Materials Solution),该解决方案将六种不同的技术整合到一个高真空系统中,其中包括一种业界首创的材料组合,可帮助芯片制造商将铜布线扩展到 2nm 节点及以下。该解决方案是一种钌和钴 (RuCo) 的二元金属组合,可同时将衬里厚度减少 33% 至 2nm,为无空洞铜回流提供更好的表面特性,并将电线电阻降低高达 25%,以提高芯片性能和功耗。

重点是改善布线并改善布线上的电介质。随着特征的缩小,将铜线放入沟槽而不产生所谓的空隙(空隙中有一部分没有铜进入)变得越来越困难。这也会影响电阻和产量。电阻问题在每一代芯片中都会再次出现。

现在,该公司正改用钌和钴的组合作为铜和薄膜之间的衬里。它可以将衬里厚度减少多达 33%。结果是沟槽中有更多的空间容纳铜,从而加宽了有效导线,降低了电阻。性能提高了。结构中这些部分的宽度是微观的,因此良率更高。

所有领先的逻辑芯片制造商均已采用采用 Volta 钌 CVD(化学气相沉积)技术的全新 Applied Endura 铜阻挡层种子 IMS,并已在 3nm 节点开始出货。

三星电子副总裁兼代工开发团队负责人 Sunjung Kim 在一份声明中表示:“尽管图案化技术的进步推动了器件的持续微缩,但其他领域仍存在重大挑战,包括互连布线电阻、电容和可靠性。为了克服这些挑战,三星正在采用多种材料工程创新,将微缩的优势扩展到最先进的节点。”

台积电执行副总裁兼联席首席运营官 YJ Mii 在一份声明中表示:“半导体行业必须在节能性能方面实现大幅改进,以实现人工智能计算的可持续增长。”“降低互连电阻的新材料将在半导体行业中发挥重要作用,同时还有其他创新可以提高整体系统性能和功率。”

不断增长的布线机会

应用材料公司是芯片布线工艺技术的行业领导者。从 7nm 节点到 3nm 节点,互连布线步骤增加了约三倍,应用材料公司提供的可用市场机会从每月每 100,000 片晶圆 (100K WSPM) 的绿地产能增加 10 亿美元以上,达到约 60 亿美元。

展望未来,背面供电技术的引入预计将使应用材料公司的布线机会每 100K WSPM 再增加 10 亿美元,达到约 70 亿美元。

英特尔最近谈到的一项研究计划重点是改善芯片背面的布线,而芯片背面通常不用于布线。这种架构变化将电源线从芯片正面引到背面,而背面的布线需要更粗。但正面的布线也需要改进,因此这些改进都是同时进行的,Jansen说。

Jansen 表示,增加背面布线可降低复杂性,有助于实现更高效的布线以及更好的性能和功耗。但正面的改进也是实现扩展的必要条件。

大约 20 年前,布线材料从铝转变为电介质和铜。为了每年提高性能,业界一直在添加更多材料,以制造更坚固、更节能的布线。芯片设备在芯片表面的薄膜上蚀刻沟槽和通孔,然后最终用铜填充这些间隙进行布线。铜是传导电子通过芯片的主要方式。现在,这些材料充当铜和电介质之间的屏障,使它们不会相互污染。

“如果没有材料创新,屏障和衬垫将开始占据越来越多的沟槽体积。因此,这种缩放带来了一些不同的挑战。随着铜线微缩,电阻上升。这是一种基本的物理学(事实)。更细的电线将产生更高的电阻。没有很好的办法解决这个问题,”Jansen说。

他补充道:“因此,我们试图做的是增加用于转换的电线数量。其次,随着这些东西的缩小,电线之间的距离越来越近。因此,它们周围的介电体空间就越来越小。结果,就会出现电串扰。信号可能会延迟、失真,总之,性能和功耗都会降低。所以,这与我们的目标正好相反。”

为了增强对AI芯片的要求,其性能和效率必须不断提高。

应用材料公司发言人表示,所有这些工作都是为了制造更好的 GPU 和其他 AI 芯片,以满足未来的需求。他们认为这些布线发展有助于芯片行业保持每两年三次提高能源效率的趋势。

Jansen 表示:“这是一项推动 2nm 及以上技术发展的技术。”

Bhatnagar 补充说,堆叠存储芯片是将数据传送给 AI 处理器的必要条件,而 3D 堆叠能力需要较高的机械强度。这项技术使芯片能够达到较高的计算性能而不会熔化。

Bhatnagar说:“这是我们推动这些材料的原因之一——因为人工智能需要高带宽内存。”

因此,Jansen 表示,“我认为新技术继续延续摩尔定律的节奏以及单位面积晶体管密度的提高与该定律保持一致”,预计 GPU 晶体管数量将达到万亿。Nvidia 的 Blackwell 上大约有 2080 亿个晶体管。

参考链接

https://venturebeat.com/ai/applied-materials-reveals-chip-wiring-innovations-for-energy-efficient-computing/

文章来源: 半导体行业观察

- 还没有人评论,欢迎说说您的想法!